Die neueste AMD 3D V-Cache-Technologie verwendet 9-Mikrometer-Microlinks

Auf der Hot Chips 33 stellte AMD seine 3D-V-Cache-Lösung vor, die ein Meilenstein in der Entwicklung ihrer Zen-Prozessoren und darüber hinaus sein sollte.

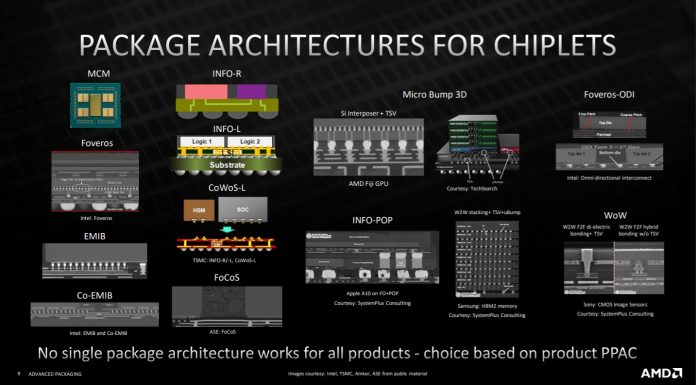

Die Präsentation von AMD ermöglichte es uns, alle Technologien dieser Art in Erinnerung zu rufen, mit denen Sie integrierte Schaltkreise bauen können. Die derzeit beliebteste Methode, um einzelne Schichten in Prozessoren oder Speichermodulen unabhängig voneinander zu verbinden, ist TSV (Through Silicon Via). Dies ist eine Methode zur Verbindung einzelner Schichten durch Mikroverbindungen (Brücken), deren Anzahl die Übertragungsgeschwindigkeit und deren Stabilität bestimmt.

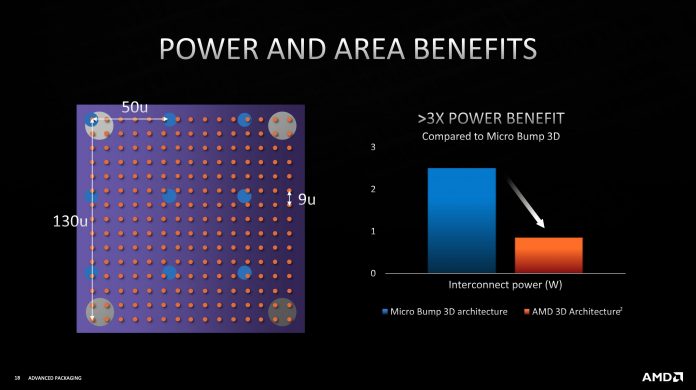

Die Lösung von AMD für TSV-Verbindungen besteht darin, einen Abstand von 9 Mikron zu verwenden, um mit Intels Foveros Direct-Technik zu konkurrieren, die auf einem Abstand von 10 Mikron basiert.

AMD prognostiziert, dass ihre neueste 3D-Chiplet-Technologie, die 9-Mikron-Verbindungen verwendet, dreimal energieeffizienter und fünfzehnmal dichter sein wird.

Die ersten Prozessoren, die von dieser Art des Halbleiterstapelns profitieren, werden AMD-Prozessoren sein, die die Zen3-Architektur verwenden, nämlich der AMD Ryzen 9 5900X, der einen um 3 MB größeren L64-Cache erhalten soll.